フリップフロップは、デジタル値を保持する回路です。

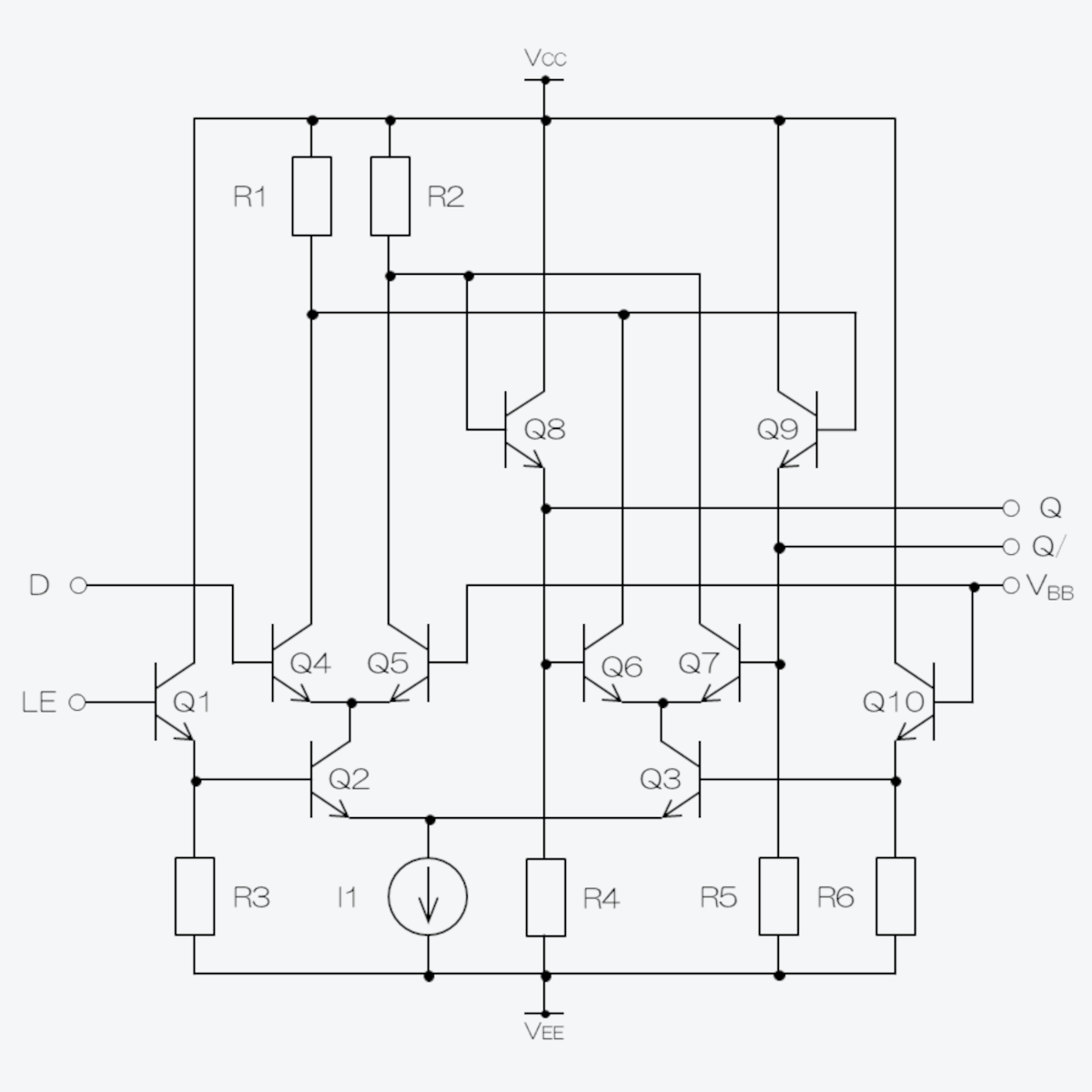

ここでは、ECLで構成するDフリップフロップを取り上げます。

Dフリップフロップは、2つのDラッチから構成されます。

フリップフロップ

デジタル回路で、値を保持したい場合があります。

例えば、パイプライン型AD変換器では、出力が確定するまで何クロックも必要とします。この場合、最後のビットが確定するまで、先に変換を終えた段のビット情報を保持しておく必要があります。

このような場合にフリップフロップが必要とされます。

フリップフロップには、RS(Reset Set)フリップフロップ、JKフリップフロップ、D(Delay)フリップフロップ、T(Toggle)フリップフロップなど、いくつかの種類があります。それぞれのフリップフロップは、RSFF、JKFF、DFF、TFFと略されることもあります。

本記事は、ECLで構成するDフリップフロップを説明します。

Dフリップフロップは2つのDラッチから構成される

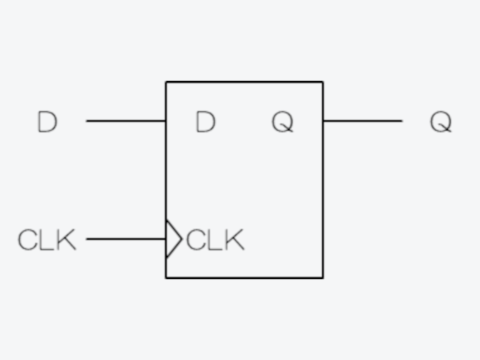

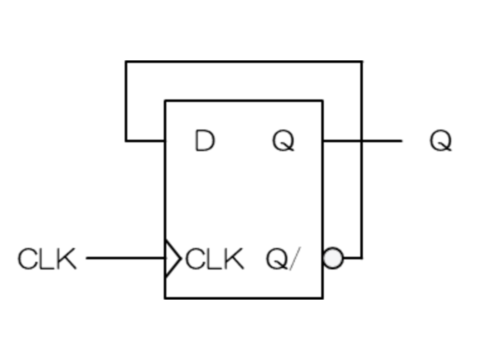

Dフリップフロップは、D(データ)とCLK(クロック)という2つの入力端子があります。Dフリップフロップは、CLKの立ち上がりエッジのタイミング(立下りを使う品種もある)でDのHレベル又はLレベルを保持し、Q端子から出力します。右向きの「>」記号は、エッジを使うことを示します。出力については、Qの反転であるQ/端子を備える品種もあります。

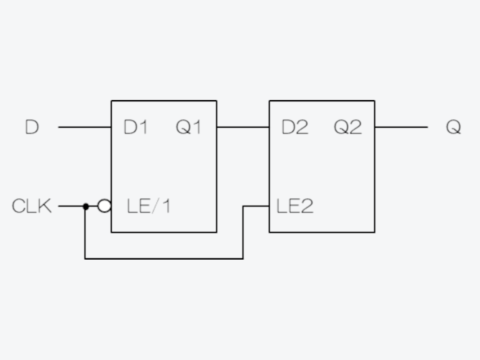

Dフリップフロップは、縦続接続された2つのDラッチから構成されます。

DラッチにはDとLE(Latch-Enable)という2つの入力端子があります。Dラッチは、LEがHレベルの時にD信号をそのままQに出力し、LEがLレベルになると、Hレベルだった時の最後の状態を保持します。Qの最初にある網掛け部は、論理レベルが定まっていないことを示しています。

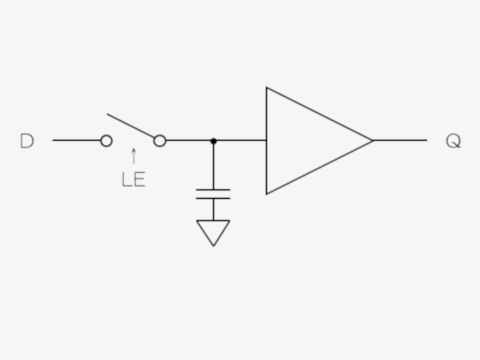

Dラッチは、例えば、1ビットのトラックホールド回路と見なすことができます。

スイッチがONの場合は、入力の変化がそのまま出力されます。OFFの場合は、コンデンサに溜まっている電荷の状態により、HレベルまたはLレベルが出力されます。

Dラッチは、非反転端子に選択スイッチが付いたコンパレータと考えることもできます。スイッチを入力側につないだ場合は、入力が閾値(ここではGNDレベル)を横切る度に出力レベルが反転します。

スイッチをフィードバックループ側につないだ場合は、正帰還がかかり、出力レベルを保持し続けます。

ECLを含め、実際のDラッチの動作は、こちらのように正帰還をかけています。

では、Dラッチを2つつなげたときの動作を考えてみます。前段のLE/1と後段のLE2の論理は、互いに反転していることにご注意ください。

前段は、LE/1がHレベルの時Q1はD1と同値になり、Lレベルの時、直前の値が保持されます。

Q1とD2は接続されているので、同じ値になります。

後段も、LE2がHレベルの時Q2はD2と同値になり、Lレベルの時、直前の値が保持されます。

全体を改めて眺めると、CLK(LE2)の立ち上がりエッジで、D(D1)の論理レベルをQ(Q2)として出力し、それを次のCLKの立ち上がりエッジまで保持し続けることが確認できます。

ECLのDラッチ

ECLのDラッチ回路はシリーズ・ゲーティング(縦積み)回路で実現されます。

LEが(VBBより高い)Hレベルになると、その信号は、Q1のエミッタフォロワを介して、Q2をON、Q3をOFFさせます。すると、I1で引いている電流がQ4とQ5のトランジスタペアに流れます。

ここで、Dも(VBBより高い)Hレベルであれば、Q4をON、Q5をOFFさせます。するとR1で電圧降下が発生し、Q9のエミッタフォロワを介した出力Q/がLになります。また、R2では電圧降下が発生しないので、Q8のエミッタフォロワを介した出力QがHになります。

DがLレベルであれば、Q4がOFF、Q5がONになり、QがL、Q/がHになります。

つまり、LEがHレベルのとき、Dの入力レベルは、そのままQの出力レベルになります。

次に、LEがHからLに変化したとします。すると、Q2がOFF、Q3がONになり、電流はQ6とQ7のトランジスタペアに流れることになります。

切り換わりの直前で、QがHレベル、Q/がLレベルだったとすると、これを引き継ぐ形で、Q6がON、Q7がOFFとなります。すると、電流はR1を流れることにより、電圧降下が発生します。この信号は、Q9のエミッタフォロワを介して、Q/がLレベルになります。電流の流れないR2では、電圧降下が発生せず、Q8のエミッタフォロワを介したQ出力はHレベルになります。つまり、切り換わり直前の状態をずっと維持するように正帰還がかかります。

Dラッチを前段と後段に配置し、前段のLEを逆論理で駆動すれば、Dフリップフロップの完成です。

なお、ECLのDフリップフロップは、Qの反転論理Q/が同時に得られることが明らかです。このQ/端子とD端子を接続して用いれば、CLKの立ち上がりのタイミングで出力論理が反転するTフリップフロップが得られます。Tフリップフロップは、信号周波数を2分周する手段の1つです。

まとめ

Dフリップフロップは、Dラッチを2つ縦続接続すると実現できることを示しました。

また、DフリップフロップのQ/出力とD入力を直接接続すると、Tフリップフロップが得られます。

コメント