ΔΣ型の1bit ADコンバータ

ΔΣ型の1bit ADコンバータ(ADC)は、オーディオ等の分野でよく用いられています。

僕は、1bitで諧調豊かな音楽が記録・再生できる原理が分からず、ずっと不思議に思っていました。でも、これは、パルス密度変調という方法を使っているんですね。つまり、振幅が0の時に0000…、フルスパンの時に1111…、その中間の時に1010…としているんです。

アナログに直す時は、いろいろな技を使うこともできそうですが、単純にLPFを入れるという手も使えます。頭いい人が考えたんだなぁ。

ΔΣ型の1bitのADCは、積分器と量子化器等で構成されています。

アナログ入力と1 bit DACの差をとるところがΔ、積分器がΣで、ΔΣ型らしいです。

普通、このブロック図だけ見せられて、理論がどうのこうのと講釈が始まります。でも、具体的な動作イメージがつかめますか?僕には無理だな。

ΔΣ型ADコンバータのExcelによる動作シミュレーション

実は、Excelを使えば簡単にシミュレーションすることができます。

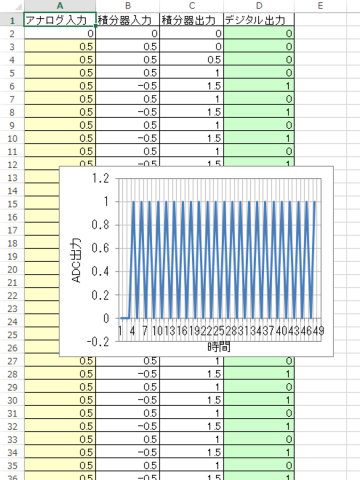

先ず、第1行目はタイトル行として、A1からD1に、アナログ入力、積分器入力、積分器出力、デジタル出力と書きましょう。

第2行目は、初期値とします。A2、C2、D2は0を入れましょう。

B2の積分器入力は、アナログ入力と、デジタル出力をアナログ値に直した値の差になります。ここでは、デジタル出力をアナログ値に直しても値が変わらないことにして、「=A2-D2」とします。さらに、このB2の式をB3~B50くらいまでコピーしましょう。コピーする行数はお好みで変えていただいて構いません。

第3行目からは積分器出力とデジタル出力を書いていきます。

積分器出力のC3は、前回の値であるC2に、そのときの入力値B2を加えればよく、「=C2+B2」となります。

デジタル出力であるD3は、積分器の出力C3をある閾値で、0と1に量子化します。ここでは、閾値を1とします。すなわち「=IF(C3<=1,0,1)」となります。

出来上がったB3,C3をB4~C50くらいまでコピーします。準備はこれで終了です。

では、アナログ入力として、フルスパンの真ん中の値である0.5をA3~A50に入れてみます。

そうすると、デジタル出力の5行目くらいから1と0が交互に表れます。積分が定常状態に達するまで、少しタイムラグがあるということになります。

アナログ入力として0.1を入れると、10行に1回、1が発生することが分かります。

A列に正弦波など、いろいろな波形を入れて挙動を確認してみてください。

また、量子化の閾値を変えたり、量子化後の値を0と1でなく、0と2にしてみるなどして、遊んでみて下さい。

おまけ(Δ型)

ΔΣ型は、Δ型を原型としています。

その構成はこちら。

積分器がフィードバック系の中に入っています。このため、デジタル出力をアナログに変換する系にも積分器が必要になります。

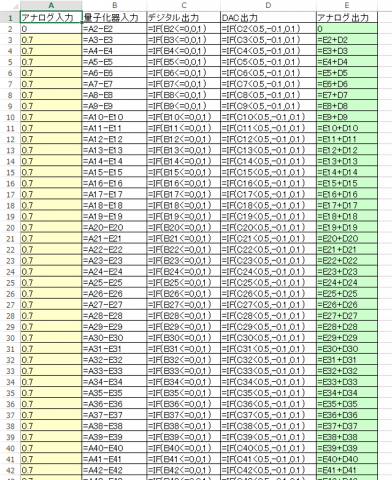

Δ型をシミュレーションするExcelのシートを示します。

量子化器には、正と負の値が入って来ることから、デジタル出力を計算する式の閾値は0です。

デジタル出力は、一般的な値である0と1で表現しました。

DACは、0と1をそのまま出力すると、実際の積分器ならいずれ飽和してしまいます。そのため、負の値も出力します。また、DAC出力の値が大きすぎると積分した値の変動が大きすぎて入力値に追随できなくなるので、±0.1の出力としました。

ここでは、入力に0.7を入れてみました。

デジタル出力は、アナログ出力が0.7に近付くまでずっと1を出し続け、0.7付近になったところで、0と1を交互に出力するようになります。

仮に、0.7に近付くまでの間に、送信ルートに雑音が発生して、1が0に変わってしまうと、0.7に近付くことなく、0.5付近でアナログ出力が定常状態になってしまいます。

このようなシミュレーションをすることで、「デルタ変調は入力信号の微分値を運んでいるから、受信パルス列を積分することによって原信号を再現する。このために伝送の途中で誤りがあると、後々までそれが影響するのが問題とされていた。」1)という発明者の一文がすっと理解できるようになりました。

1)安田靖彦:技術の生みの親・育ての親、郵政研究所月報、No.155、2001.8

コメント