1.5 bitパイプライン型ADC(analog to digital converter、アナログ・デジタル変換器)の動作原理って理解できますか?

僕は、頭の中だけでは理解できなかったので、Excelを用いて動作をシミュレーションしてみました。

1.5 bitパイプライン型ADCの1段分の構成

パイプライン型ADCは、多段構成です。

各段は、T/H(トラックホールド)回路、ADC、DAC(digital to analog converter)、アナログ加算器、2倍のアンプから構成されます。

入力のレベルは説明の都合上、-1~1とします。ただし、回路のオフセットやゲインを調節すれば、自由に設定できます。

T/H回路は、一段の処理が終わるまでの間、入力値を保持します。

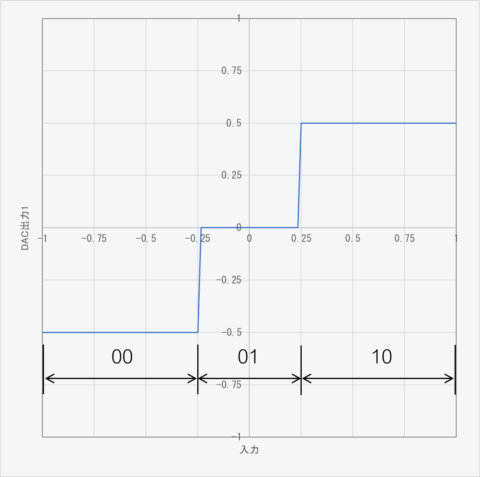

ADCは、アナログ値をデジタル変換します。1.5 bitパイプライン型では、00、01、10の3値のデジタル出力が出ます。ただし、後述のように、切り換わりの閾値が特別です。

DACはデジタル値をアナログ値に変換します。00、01、10のデジタル値はそれぞれ-0.5、0、0.5のアナログ値を出力します。

〇印の付近に+と-が示されている箇所はアナログ加算器です。DAC出力は、負の値にしてから加算するので、結果として、T/H回路出力とDAC出力の差信号を出力します。

2倍のアンプは加算器の出力を2倍します。

Excelによる動作シミュレーション

1段目のシミュレーション

早速、Excelによる動作シミュレーションをしてみます。

先ず、タイトルを入力します。A1~G1に、それぞれ「分割数」「入力」「TH出力1」「ADC出力1」「DAC出力1」「加算器出力1」「アンプ出力1」と入力してください。カラム名の最後に付いている「1」という数は、1段目を示しています。

次にA2セルに64とでも打ちましょう。これは、0~1のアナログ入力を分割する数です。値を大きくすれば、グラフがきれいに描けます。64という値は、2段分の動作が理解できる程度の最低限の分解能といった値です。必要に応じて増やしてください。

この分割数に「n」という名前を付けましょう。

A2セルを選ぶと、左上に「A2」と表示している欄があると思います。これに「n」と入力してEnterを打ってみましょう。これで、A2セルに入っている値を「n」として扱うことができるようになりました。

続いて、B2の欄に「=(ROW()-2-n)/n」と入力してEneterを打ちましょう。値が「-1」になったでしょうか?改めてB2セルを選択すると、セルの右下が、小さな■になっていると思います。それを130行までドラッグしてください。そうすると、B2セルがコピーされることにより、-1~1の数列ができると思います。

B列にも名前を付けます。

セルの上で、A、B、C、…と表示されているところの「B」を選ぶとB列全体が選択されます。このとき、左上の欄には「B1」と表示されていると思います。ここに「入力」とタイプしてEnterを押します。すると、B列全体が「入力」という名前になります。

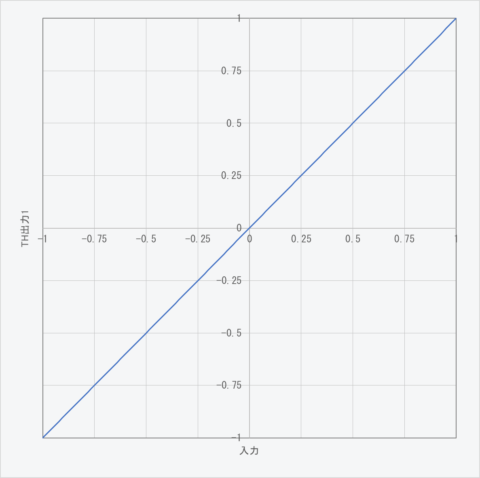

次に、C列に移ります。C列は、T/H回路の出力であり、入力と同じ値となります。

わざわざこの列を作らなくても構いませんが、グラフを描くときに便利です。

C2の欄に「=入力」と入力してEnterを打ちましょう。値が「-1」になったでしょうか?改めてC2セルを選択すると、セルの右下が、小さな■になっていると思います。その■をダブルクリックしてください。そうすると、C2セルの内容がC130までコピーされ、-1~1の数列ができます。B列と同様の手順により、C列全体には、TH出力1という名前を付けてください。

D列はADCの出力です。このADCは、閾値が特別です。定義域を8等分して、左から3つ分が00、中2つ分が01、右3つ分が10になります。今、定義域が-1~1ですから、8等分すると1つ分は0.25です。したがって、-1~-0.25が00、-0.25~0.25が01、0.25~1が10となります。

これを数式で示すと、「=IF(TH出力1<=-0.25,”00″,IF(TH出力1<0.25,”01″,”10″))」となります。今は、動作の概要を知りたいだけなので、不等号は適当に付けています。厳密性を追求したい場合は各自でお考え下さい。

この式をD2からD130まで入力し、D列全体に「ADC出力1」と名前を付けてください。

E列は、ADC出力をDA変換した結果です。前述のように、00、01、10のデジタル入力に対するアナログ出力は、それぞれ-0.5、0、0.5です。

これを数式で示すと「=IF(ADC出力1=”00″,-0.5,IF(ADC出力1=”01″,0,0.5))」となります。この式をE2からE130までコピーして、E列全体に「DAC出力1」と名前を付けてください。

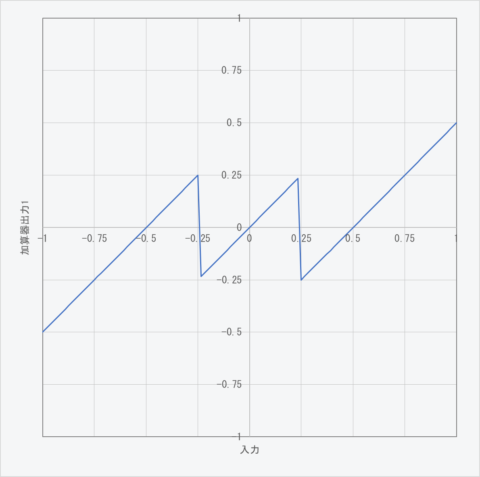

F列は加算器の出力です。TH出力と負号を付けたDAC出力を加算します。つまり、差になります。式は「=TH出力1-DAC出力1」となります。これもF2からF130までコピーして、F列全体に「加算器出力1」と名前を付けてください。

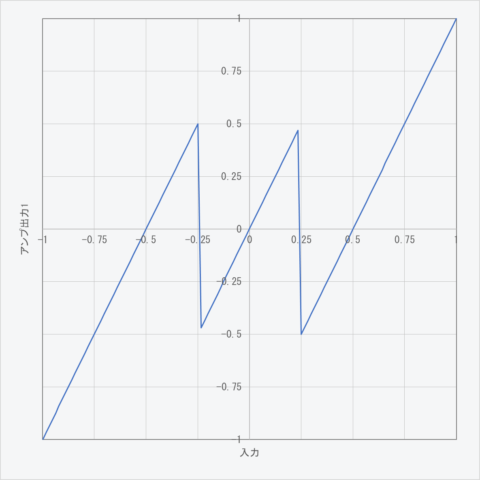

G列は2倍アンプの出力です。加算器出力1の値を2倍するので、式は「=加算器出力1*2」となります。これもG2からG130までコピーして、G列全体に「アンプ出力1」と名前を付けてください。

よく見かけるグラフになってきました。

2段目のシミュレーション

図3に示した-1~1の単調増加のT/H出力が、図6に示すアンプ出力1になりました。

2段目は、このアンプ出力1を入力として考えます。

全体を一度に考える前に、先ずは3領域に分割して概形を考えてみましょう。すなわち、アンプ出力1が-1~0.5の領域(入力としては-1~-0.25)、-0.5~0.5の領域(同-0.25~0.25)、-0.5~1の領域(同0.25~1)に分割してみます。

アンプ出力1が-1~0.5の領域だけ抜き出してみると、

となります。つづいて、-0.5~0.5だけ抜き出してみると、

となります。最後に、-0.5~1を抜き出してみると、

となります。

第2段目の出力は、これを横につなぎ合わせた形になるので、-1から増加し、-0.5と0.5の間で行き来を繰り返し、最後が1になって終わることが分かります。

では、第2段目について、Excelシートを作っていきましょう。

まず、C1:G2の領域をコピーします。次に、H1セルを選択し、ペーストします。

さらに、1行目のタイトルに含まれている1の文字を2に変更します。すなわち、H1からL1のセルの値を「TH出力2」「ADC出力2」「DAC出力2」「加算器出力2」「アンプ出力2」とします。

次いで、H列からL列のそれぞれに、今変更した名前を付けます。

さらに、Hを「=アンプ出力1」に変更し、I2からL2は、式中の名前の1を2に変更します。すなわち、順に「=IF(TH出力2<=-0.25,”00″,IF(TH出力2<0.25,”01″,”10″))」「=IF(ADC出力2=”00″,-0.5,IF(ADC出力2=”01″,0,0.5))」「=TH出力2-DAC出力2」「=加算器出力2*2」とします。最後に、H2:L2を選択し、L2セルの右下の■をダブルクリックすると、L130まで値が入ります。

入力を横軸に、アンプ出力2を縦軸にしてグラフを描くと図10になります。

さて、図10の下部に、1段目のADC出力を黒字で示しました。また、2段目のADC出力を青字で示しました。

ここで、1段目のMSB(Most Significant Bit、最上位ビット)を22の位、1段目のLSBと2段目のMSBを21の位、3段目のLSBを20の位と見なします。すると、表1に示すように、3 bitのADC出力が得られます。

出力が010と100については、それぞれ2通りの組み合わせがあります。ただ、図10を見ると、それらの組み合わせの幅は、他の組み合わせの幅に対して1/2であり、1つのコードに対するアナログ入力の幅は均等ということが分かります。ただし、000と110については、例外で1.5倍の幅になります。また、このため、111というコードが発生する余地がありません。

| 表1:全体のADC出力 | ||

| 1段目 | 2段目 | 全体のADC出力 |

| 00 | 00 | 000 |

| 00 | 01 | 001 |

| 00 | 10 | 010 |

| 01 | 00 | 010 |

| 01 | 01 | 011 |

| 01 | 10 | 100 |

| 10 | 00 | 100 |

| 10 | 01 | 101 |

| 10 | 10 | 110 |

まとめ

1.5 bitパイプライン型ADCをExcelでシミュレートしてみました。

自分の手を動かしてみて、ようやく動作が分かりました。初めに考えた人は聡明だと思います。

分解能nの数を増やせば、もっときれいな図が描けます。また、興味があれば、段数を増やしてみてください。

1.5 bitパイプライン型ADCは、もともと、比較器のオフセットばらつきに起因するビット欠けを無くすために考案されました。本記事で、動作原理が理解できましたら、そちらの理屈についても考えてみてはいかがでしょうか?

コメント