ECL(Emitter Coupled Logic)は、昔、スーパーコンピュータなどに使われていた高速ロジックです。昨今は、CMOSが高速動作するようになったため、絶滅危惧種です。でも、ON Semiconductor社による販売は続いていますので、どこかに生息はしているようです。

本記事はECLの動作概要を説明します。

ダイオードで考えてみる

ECLはバイポーラトランジスタで構成する論理回路です。

バイポーラトランジスタの基本はPN接合ダイオード(以下ダイオード)ですので、先ずはダイオードで考えてみます。

ダイオードには2つの端子があり、電流が流れ込む方をアノード、電流が流れだす方をカソードと言います。(あいうえお順に並べると、アノードの方が先に来るので、アノードからカソードに流れると覚えます。英語のAnodeとCathodeでも、ABC順に並べると、Anodeの方が先に来るので、やはり、この覚え方が使えます。)

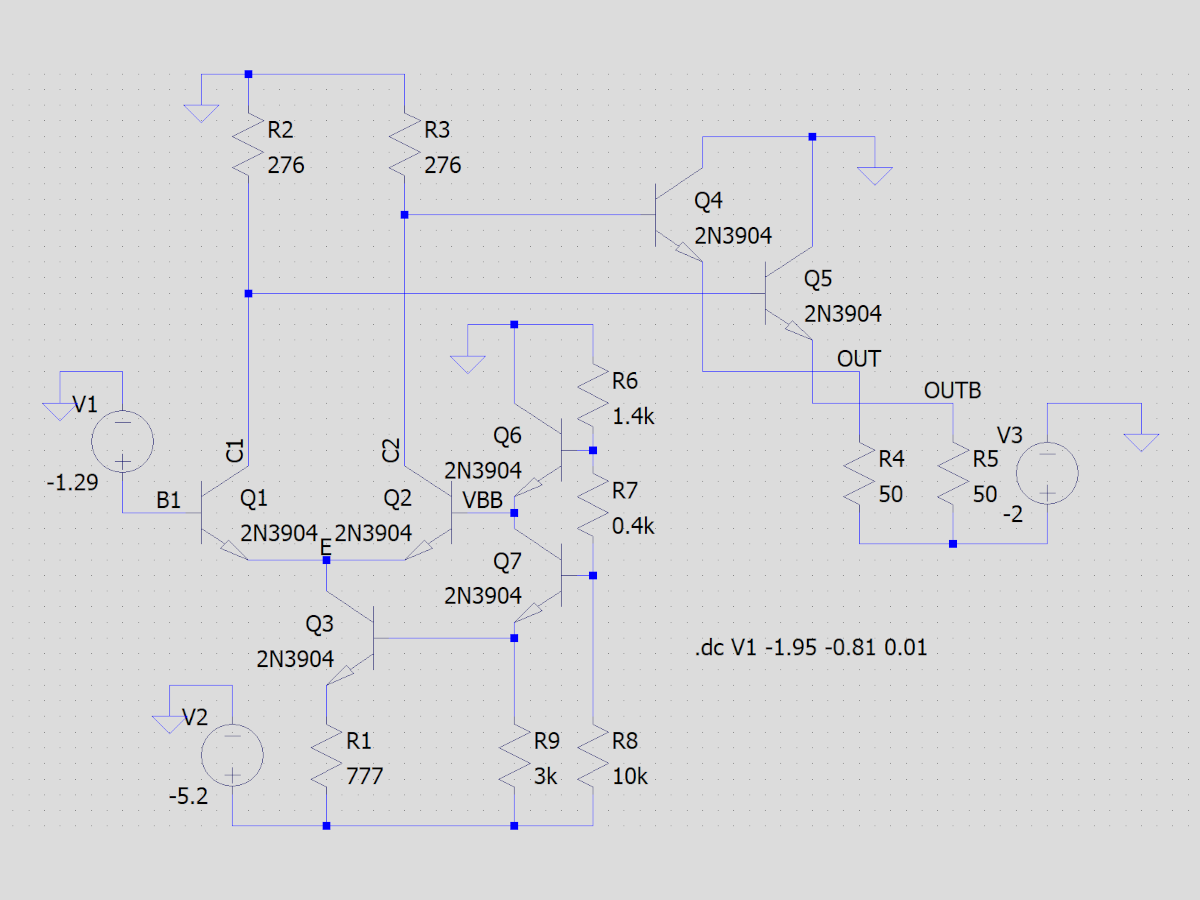

ダイオードのI-V特性を単純化すると、こちらの記事に示したように、

(1) ![]()

となりますので、アノードとカソードの間に電圧をかけていくと、0.6Vくらいから急に電流が流れ始めます。

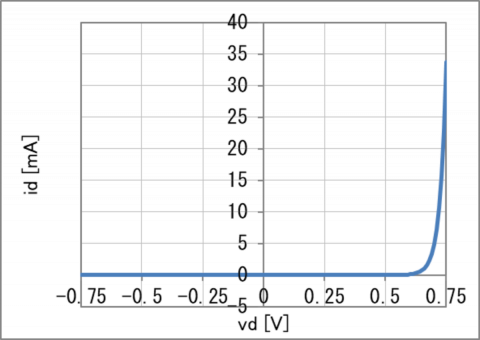

さて、ここで、2つのダイオードD1、D2のカソード同士を接続することにします。さらに、このカソードの接続点には、400μAの電流源をつなぎます。

アノード側は、2つのダイオードにかける電圧を変えるため、電圧源V1を介してお互いを接続します。ただ、V1だけだと、D1、D2に合計400μAの電流を流す経路が無いので、抵抗R1、R2を使って、グラウンドから電流が流れるルートを作ります。

(ここでは回路の対称性を考えて、抵抗を2本使いました。でも、電流経路ができれば良いだけなので、どちらか1本でも問題ありません。また、抵抗値も0Ωでなければ適当で構いません。)

電圧源V1の値を-1V~1Vに変化させてDC解析してみると、100mVくらいの電圧差があれば、電流が切り換わることが分かります。

片方のダイオードに600mVくらいの電圧がかかり、もう片方のダイオードが500mVくらいの電圧になると、電圧の低いダイオードには電流がほとんど流れなくなります。このスイッチング動作が、ECLの原理です。

ECLを大信号等価回路で考えてみる

ここでバイポーラトランジスタの大信号等価回路を考えてみます。

バイポーラトランジスタの大信号等価回路は、ベース・コレクタ間のダイオードと、ダイオードに流れる電流をβ倍した、コレクタ・エミッタ間の電流制御電流源で表されます。βは普通、100程度です。

では、先の回路のダイオードをベース・エミッタ間のダイオードとみなし、これに電流制御電流源を付け加えて、トランジスタの等価回路にしてみましょう。

LTSpiceの電流制御電流源(F)は、電圧源を流れる電流を検知して動作します。ここではD1とD2に流れる電流を検出したいので、0Vの電圧源であるV2とV3をそれぞれ直列に接続しました。

F1、F2はV2、V3の電流をそれぞれ100倍するように設定してあります。これにより、電流の駆動能力が約100倍に高まったので、一番下の電流源を400μAの100倍である4mAにしました。

また、増幅された電流を検出する負荷抵抗として、250ΩのR3、R4を配置しました。

電流を検出したときの電圧OUT、OUTBとしてを図示すると、±100mVのところで、電圧値が切り換わります。先に示した電流の結果とよく似ています。

振幅は、約1V取れていて、これが論理振幅になります。

ECLのDC解析

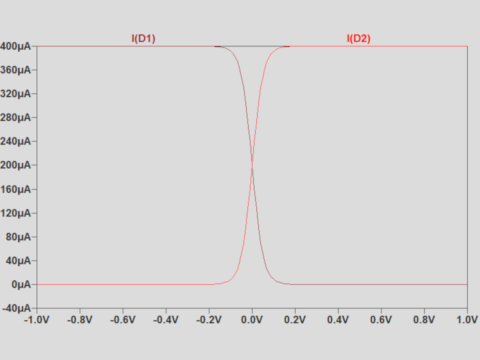

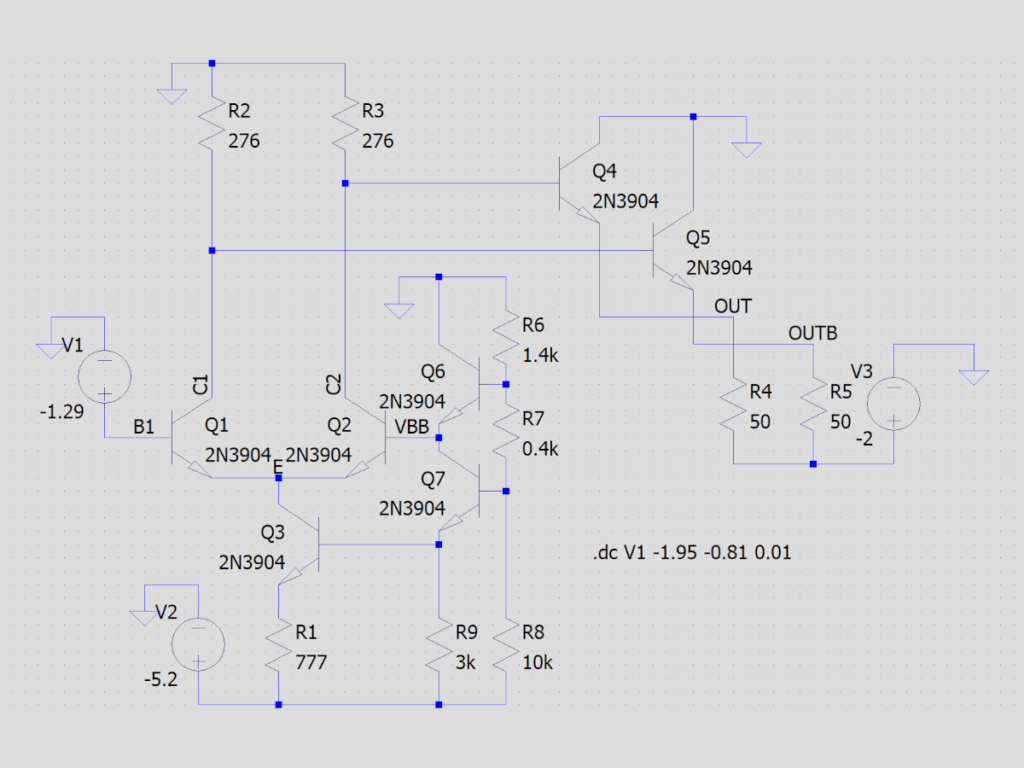

では、実際にトランジスタで表してみます。

だいぶ複雑になりました。

等価回路のD1、F1がQ1、D2、F2がQ2に相当しています。

このQ1とQ2のエミッタが結合していることから、Emitter Coupled Logic(ECL)と称されます。

電流源I1はQ3とR1で構成されます。もし、電圧源や電流源の作り方について馴染みがないようであれば、こちらの記事をご覧ください。

負荷抵抗はR2とR3です。

R1、R2、R3のそれぞれ777Ω、276Ω、276Ωという値は、文献[1]から採用しました。

電源電圧V2はECLの通常動作電圧である-5.2Vとしました。

バイポーラトランジスタのモデルには、2N3904(定番の2SC1815相当)を使っています。バイポーラトランジスタの動作点は種類にあまり依存しないため、DC解析ならロジックIC内のトランジスタのモデルを使った結果と大差ない値が得られるはずです。

Q6、Q7などからなるバイアスネットワークは、論理閾値であるVBBが-1.29V、定電流源の電流値が約4mAになるように、適当に決めました。

通常のECLは、内部に論理閾値VBBを発生させる回路を有していて、(差動入力ではなく、)シングルの入力で使用します。

負荷抵抗で発生した出力のインピーダンスは250Ωです。この値は負荷抵抗値そのものです。この値はかなり高い値であって、次段の入力インピーダンスが50Ωのように低い場合、論理振幅が1/6に小さくなってしまいます。そこで、Q4、Q5を用いたエミッタフォロワにより、出力インピーダンスを下げて、(ICのECLであればパッケージ外に)OUT、OUTBとして出力します。

もし、エミッタフォロワに馴染みがないようであれば、こちらの記事をご覧ください。

出力信号OUT、OUTBは、普通、特性インピーダンスが50Ωの伝送線路で引き回します。よって、反射を起こさないようにするためには、受信端において、50Ωの抵抗負荷で終端する必要があります。もし、高速信号における反射に馴染みがないようであれば、こちらの記事をご覧ください。

出力信号は負の電圧です。そのため、終点抵抗の50ΩをOUT、OUTBとグラウンドの間に入れてしまうとQ4とQ5がオフしてしまい、エミッタフォロワとして動作しなくなります。そこで、終端抵抗は、-2Vの電圧源V3に接続し、常にQ4とQ5に電流が流れるようにします。

入出力特性を示します。

入力電圧は、-1.95Vから-0.81Vとしました。

出力電圧は、閾値電圧である-1.29Vを境として論理が反転しており、-1.77Vから-0.91Vの値を示しました。入力電圧と若干異なる値ではありますが、閾値電圧に対するマージンは十分にあるので、とくに問題にはなりません。

なお、ECLは、余計なインバータを必要とすることなく、OUTとOUTBのコンプリメンタリ出力が同時に得られるというメリットがあることを強調しておきます。

Q1とQ2のコレクタ・エミッタ間電圧(前者はV(c1)-V(e)、後者はV(c2)-V(e)として表示)は、図に示す通りで、最小値でも0.4Vあります。これは、トランジスタが飽和領域に入らないで、高速動作できることを意味します。(飽和領域に入っているトランジスタのVCEは、0.1V~0.2V程度です。)

飽和領域に入っているトランジスタの動作速度が遅くなる理由は次の通りです。

ベースは、普通、拡散電流の形で電流が流れています。つまり、エミッタからベースに注入された電子は、エミッタ側の濃度が高く、コレクタ側の端の濃度は0になります。これにより、濃度の勾配ができるので、ベースにいる電子は、濃度の薄いコレクタを目指して動くことができます。しかし、トランジスタが飽和領域に入ると、エミッタとコレクタの電位差がほぼなくなります。このとき、コレクタで電子がスムーズに回収されずに滞るようになり、ベースとコレクタの境界の電子濃度が0にならず、エミッタ側と同程度の濃度になります。つまり、ベース領域において濃度の勾配ができにくくなるので、トランジスタがOFFする際に、電子がエミッタとコレクタのどちらに動くべきかがあいまいになります。この結果、ベースに電子が長時間残ることになり、OFFするまでのスピードが遅くなります。

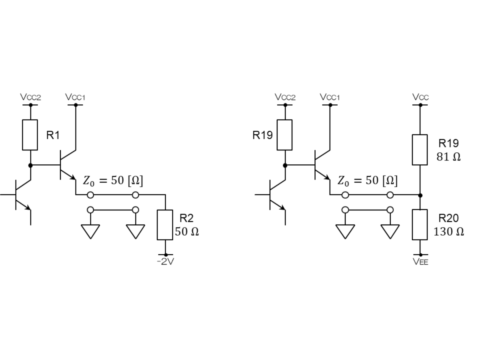

テブナン終端

上述のように、ECLは、-2Vの抵抗に50Ωの終端抵抗を接続して受信します。しかし、-2Vの電源を新たに設けることは面倒です。コストもかかります。このため、実システムではしばしばテブナン(Thevenin)終端を使います。

テブナン終端は、GND(図ではVCC)と-5.2V(同VEE)の電源を利用して終端条件を作ります。

先ず、-2Vという条件は、

(2) ![]()

です。また、50Ωという条件は、

(3) ![]()

です。これらを連立させると

(4) ![Rendered by QuickLaTeX.com \begin{eqnarray*}R_{20}=\frac{50\cdot 5.2}{2}=130\,\left[\Omega\right] \\\therefore 5.2 R_{19}=2\left(R_{19}+130\right) \\\therefore R_{19}=\frac{2\cdot 130}{5.2-2}=81.25\,\left[\Omega\right]\end{eqnarray*}](https://miscellaneous.tokyo/wp-content/ql-cache/quicklatex.com-4f3e6efa64feaa838e39ccc6314ab376_l3.png)

となります。

ディスクリート部品でテスト回路を組む場合、81.25Ωについては、E12系列の82Ωを使い、130Ωについては、同じくE12系列の390Ωを3並列で使います。こうすると、論理振幅をtyp値で考えたとき、R19の消費電力は、

(5) ![]()

であり、R20の消費電力は1抵抗あたり

(6) ![]()

となるので、1/16W(=0.0625W)のチップ部品でも動作させることができます。

ECLの過渡解析

ECLの過渡解析をしてみます。

回路図は、DC解析とほぼ同じです。ただし、V1として、幅が約50nsのパルスを入れています。シミュレーション時間は100nsです。論理振幅は、文献[1]でtypical値とされている-1.75V~-0.98Vとしました。

シミュレーションを実施したところ、論理振幅は、約-1.77V~約-0.77Vとなりました。立ち上がり時間は、約11.0nsです。Motorolaの高速ECL(10KH)の立ち上がり時間は約1.8nsですので、専用ICに比べて約1/6の速さです。ただし、今回使用したディスクリートのモデルには、パッケージなどの寄生容量としてかなり大きい値が入っているはずなので、それを考慮すると、頑張った値だと思います。

ECLとCMOSの比較

本記事の回路構成では、-5.2Vに5.6mA、-2Vに2.9mAが流れます。それぞれ、約29mW、58mWの電力を消費するので、全体で約87mWの電力を消費します。このように消費電力が大きいことがECLのデメリットです。

例えば、CMOSのインバータゲートのデータシートを見ると、3.3Vで、1μA(静的0.1μA、動的0.9μA)という値が示されており、消費電力は3.3μWです。つまり、ECLとCMOSでは消費電力が26,000倍違います。しかも、こちらのデータシートには、CMOSの立ち上がり時間が3nsなどと書いてあります。もはや、普通のシリコントランジスタで作るECLは、CMOSに太刀打ちできなさそうです。

まとめ

本記事は、ECLの動作原理を述べました。

ただ、Logicと称しながら、本記事で示した機能はバッファとインバータの機能しか示していません。論理和(OR)や論理積(AND)の実現方法については、こちらをご覧ください。

[1] William R. Blood, Jr.: MECL SYSTEM DESIGN HANDBOOK Fourth Edition, MOTOROLA INC., p.2, p.4, p.15 1988

コメント